Bei einem FPGA hängt die höchte Taktfrequenz vom langsten Pfad zwischen zwei FF ab.

f_max = 1 / t_pfad_max

Je länger der Pfad, desto tiefer die maximale Taktfrequenz.

t_pfad = 5 ns f_max = 200 MHz CLK_Bauteil = 200 MHz

t_pfad = 3 ns f_max = 333 MHz CLK_Bauteil = 333 MHz

Optimierung

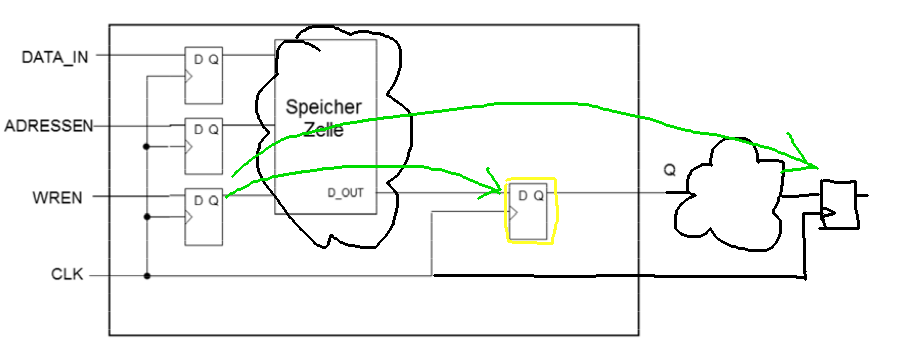

Durch das direkte Anbinden eines FF beim Ausgang eines Speichers, wird der Pfad verkürzt.

Nachteil der Optimierung

Die Datenverarbeitung braucht insgesamt einen Takt-Zyklus mehr.