Logik

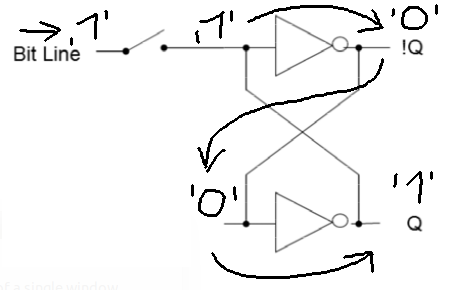

Ein FF besteht aus logischer Sicht aus zwei Invertern. Durch die zwei Inverter, erscheint der Eingangswert wieder am Ausgang. Der Wert wurde gespeichert. Tiefer betrachtet, ist die Basis eines FF ein Latch. Das Latch ist der Baustein, der durch Set-Reset am Ausgang ein Wert behält. Das Latch ist aber asynchron und deshal kein FF im engen Sinn. Das FF hat zusätzlich einen Clock. Dadurch werden erst (bei steigender Flanke) die Ausgänge gesetzt.

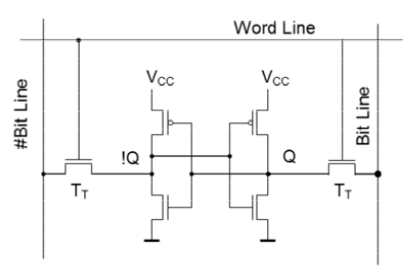

Hardware (mit Transistoren)

Pro Speicherzelle (FF) hat es zwei Bit-Lines. Eine ist die Inversion der anderen.

Auf der Bit-Line wird das aktuelle Bit gesetzt (siehe erstes Bild für Logik).

Die Word-Linien, ist die Verbindung einer Reihe von Speicherzellen.

Unterschied Transistoren <-> Kondensatoren als Speicherelement

FF können mit Transistoren (z.B. in SRAM, s = static = stabil) oder mit Kondensatoren (z.B. DRAM, d = dynamisch = instabil) aufgebaut sein. Die Transistoren behalten ihren Wert (Zustand ‚1‘ oder ‚0‘), sind sie einmal geschalten, was bei den Kondensatoren nicht gilt. Die Kondensatoren entladen sich (‚1‘ – > ‚0.7‘ -> ‚0.5‘), weshalb ihr Wert immer wieder neu gesetzt (refresh) werden muss.

Das Refrehen wird zeilenweise gemacht.

Bsp. Bei einem 16-Bit-Memory, wird in einem Refresh-Zyklus 16 FF neu gesetzt.

Gute Website zu detaillierteren Informatioenen zum digitalen Speichern („How RAM works“).