In den FPGAs sind PLLS ein Standard für zwei Gründe:

– Um Pfadverzögerungen zu Kompensieren (Bsp. 2)

– Um andere Taktfrequenzen zu erhalten (Bsp. 1)

Neuer Takt

Viele Protokole besitzen ihre eigene Takt-Frequenz. Daher braucht es einige Takte innerhalb eines FPGAs

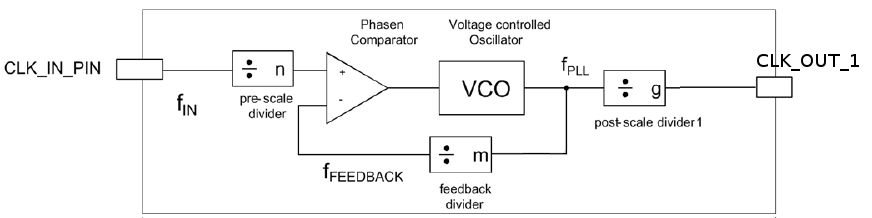

f_out = (f_in * m) / n // m wird multipliziert, n und g dividiert

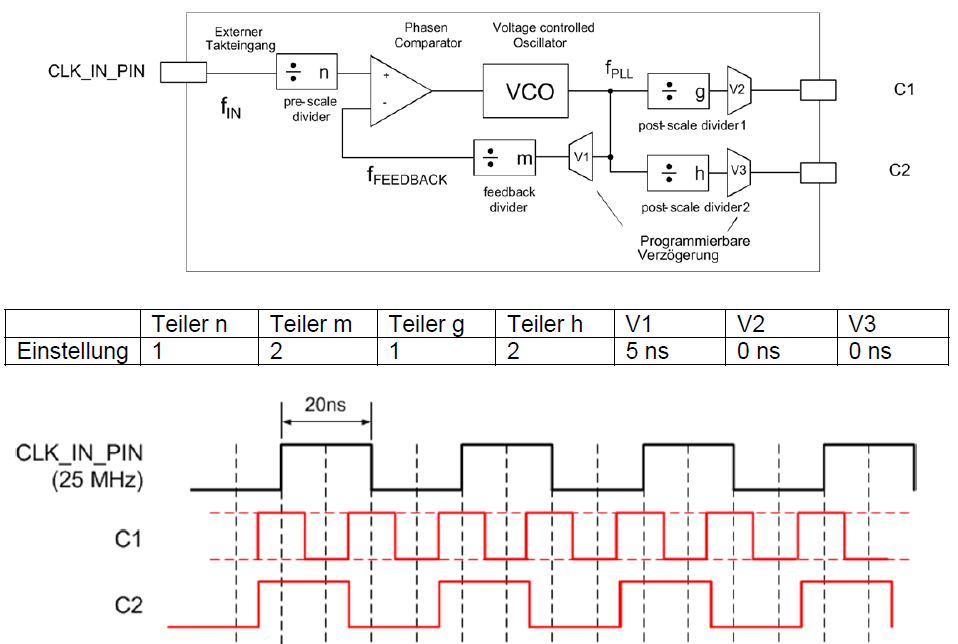

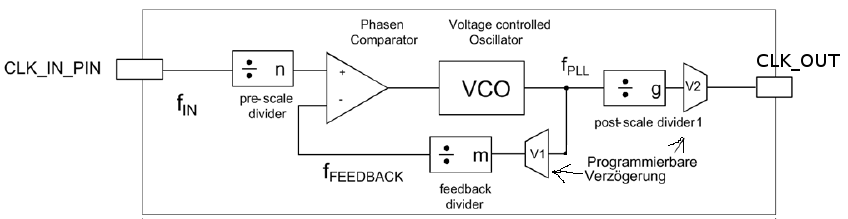

Kompensation Verzögerung

Werte im Feedback Pfad v1= 3 ns schieben CLK_IN nach vorne,

Werte beim Ausgang v2 = 8 ns verzögern CLK_IN.

Bsp Kompensation

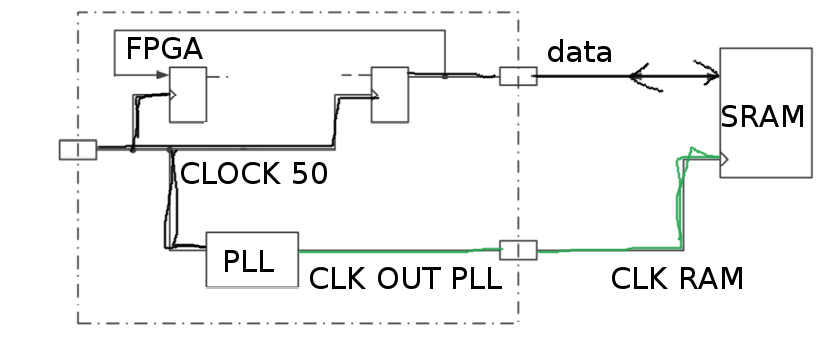

Ausgangslage: Durch Flip-Flop-Verzögerung oder Pfadverzögerung und IO-Verzögerung kommt data 5ns später als CLK_50 beim SRAM an.

1.) Entweder führt man ein PLL in den data-Pfad ein,

dann muss der PLL den CLK_50 vorverlegen v1 = 5 ns

um die Verspätung zu kompensieren,

oder (siehe Bild)

2.) man verzögert den CLK_50 zum SRAM mit genau der Verzögerung,

die der data-Pfad hat v2 = 5 ns . Dann kommt CLK RAM „gleich verzögert “

wie data beim SRAM an.

PLL Rechenbeispiel mit Takterzeugung und Verzögerung

..