Grund

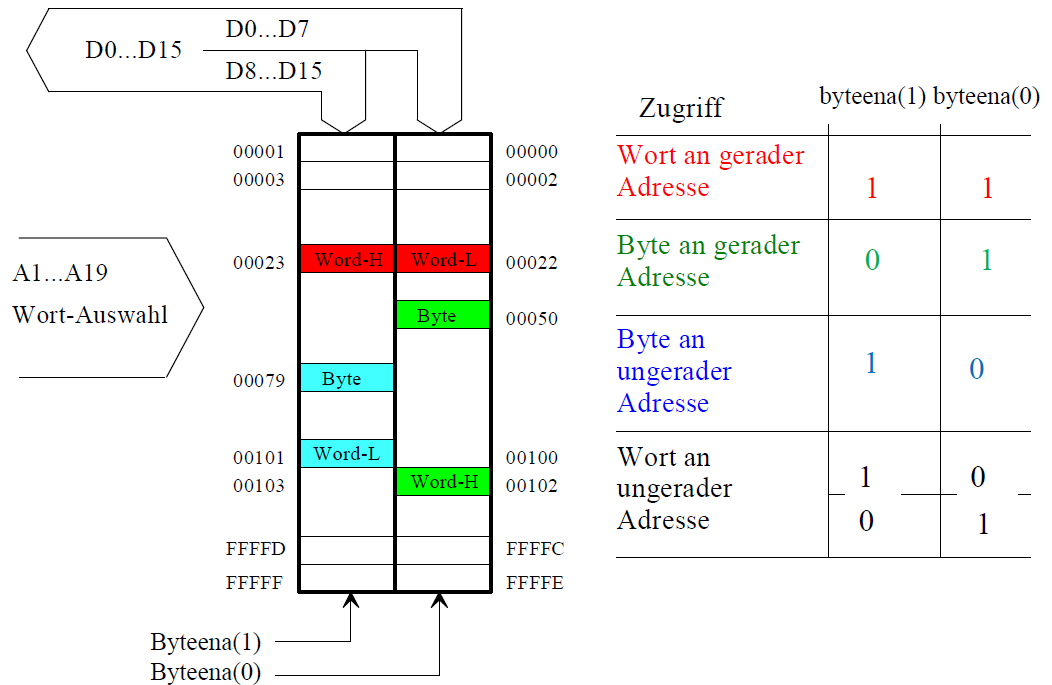

Entspricht die Speicherbreite nicht der Breite des Buses, so müssen die Bytes des Busses über enable aufgeteilt werden können.

Mit enable sagt man, ob man den ersten oder zweiten Teil der Busbreite will.

Bsp

32-Bit-System für einen Baustein nur 16 Bit (z.B. für ein IO-Port oder ein Speicherbaustein).

Byte_enable_0:

Bezieht sich auf die höheren Bits des Datan-Signals im Bus: Data[16] – Data[31]

Byte_enable_1:

Bezieht sich auf die tieferen Bits der aktuellen Busdaten: Data[0] – Data[15].

Setzt man Byte_enable_0, so werden nur die 15 oberen Bits des akutellen Bussiganals geschrieben oder gelesen.

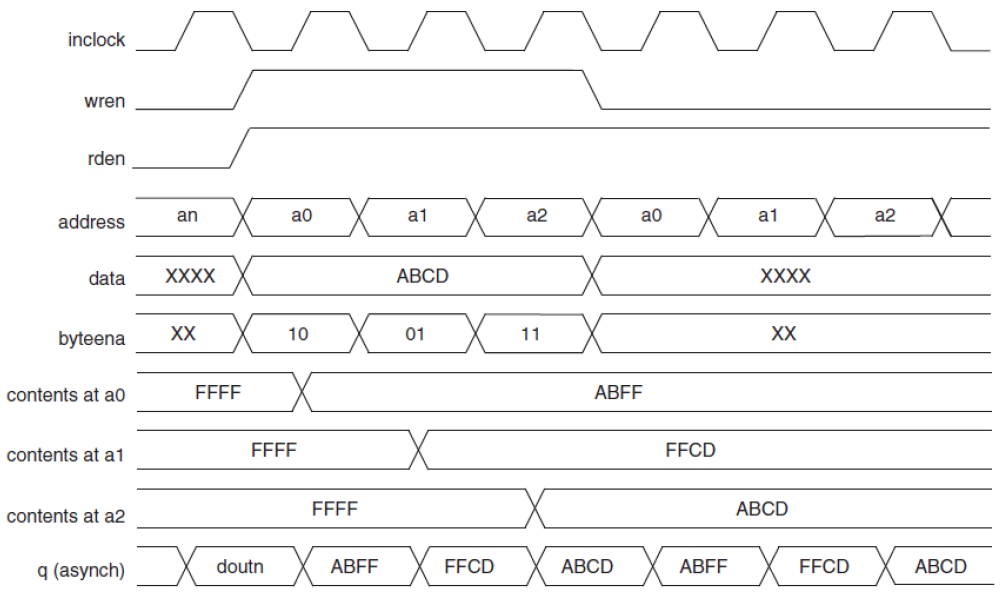

Aktuelle Busdaten und Speichervorgang

Hier liegen in einem Speicher bereits Daten an den Adressen a0, a1 und a2.

Auf dem Bus liegt ein aktuelles Datenpaket (data) von 32 Bit.

Teile (oder auch das ganze) Datenpaket sollen auf die belegten Speicheradressen geschrieben werden.

Da auch der Befehl Lesen aktiviert ist, wird „zeitgleich“ von der bestehenden Adresse auch der Wert an den Datenausgang (q) gelegt.