Funktionsweise

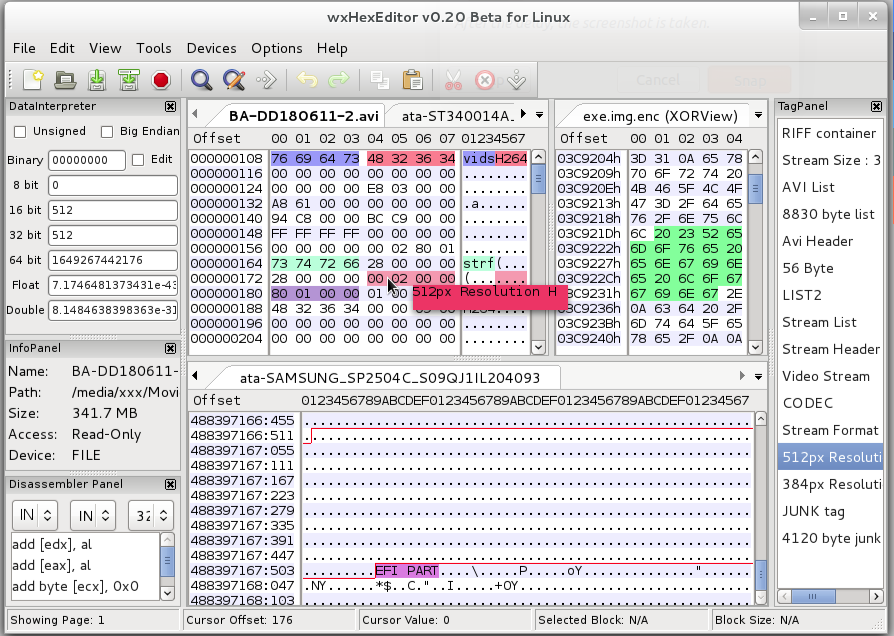

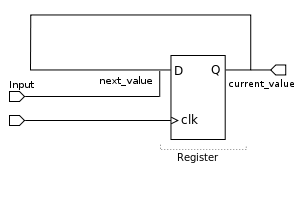

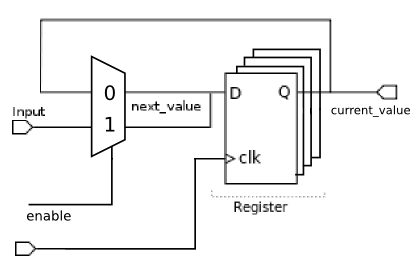

Jedes Bit wird in eine Speicherzelle (FET) gespeichert. Im Gegensatz zum FPGA ist diese Speicherzelle nicht flüchtig.

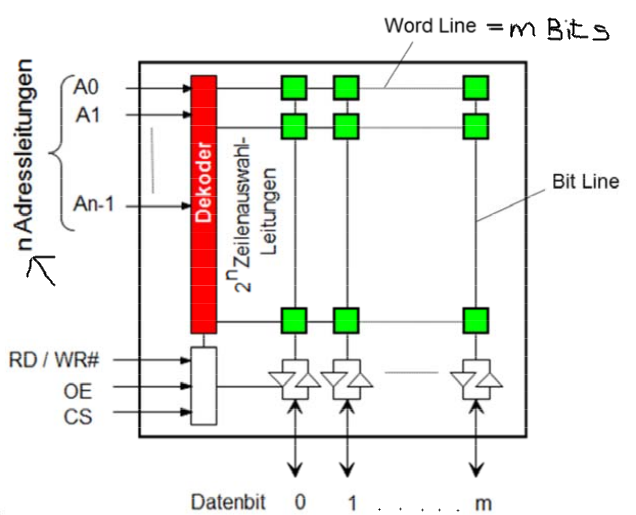

Ansteuerung

Wie bei RAMs: über eine Matrixordnung. Es wird Zeilenweise oder in ganzen Sektoren gespeichert. Jede Zeile entspricht einem Word einer bestimmten Bit-Länge.

Man spricht FLASH Speicher selten direkt an, sondern nutzt Schnittstellen.

Im Embedded Bereich

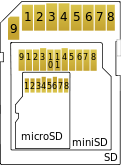

Brauchen einen externen Speicherplatz zum Speichern von Daten oder zum Booten des Betriebssystems und der Applikationen. Flash-Speicher werden ROMs vorgezogen, da man diese auswechseln kann. Dadurch ist ein Update der Firmware möglich, was beim ROM nicht der Fall ist. Eine SD-Karte (ebd. ein Flash Speicher) ist eine Alternative zu Flash-ICs.

Spezialitäten

– sind langsam

– können auch als HD-Ersatz genommen werde

– EEPROMs sind die bekanntesten Flash Speicher

– Jeder USB-Stick hat einen Flash-Speicher und einen Microkontroller