Ein Parser implementiert eine Code-Grammatik.

Für jede Regel wird eine Funktion erstellt.

Ein Parser implementiert eine Code-Grammatik.

Für jede Regel wird eine Funktion erstellt.

– alle Daten werden zu chars

– In: bedeutet von aussen zur CPU.

– out: bedeutet von OS nach aussen

————————————————————————————-

istream

char Daten werden übergeben

ostream

sendet chars an eine Ort (file, konsole, speicher, ..)

ifstream [Daten in File ablegen]

– Datei als String mitgeben

ifstream stream_a {„input.txt“}

– Inhalt wortweise in String ablegen string temp

– Strings in Vektor speichern vector <string> input

while (stream_a >> temp) {

// fill vector

input.push_back(temp);

}

ofstream [ lesen von einem file (wird als stream gemacht)]

cout << "Name of output file"

string name_outputfile;

cin >> name_outputfile;

ostream stream_1 {name_outputfile};

if (! stream_1) error("Konnte nicht eingelesen werden.");

strukturiert einlesen

struct Inputdata {

int hour;

double temperature;

};

cout << "Please enter input file name: ";

string name_inputfile;

cin >> name_inputfile;

ifstream ist {name_inputfile};

if (!ist) throw ios_base::failure("can't open input file "+name_inputfile);

vector<Inputdata> temps; // structured vector

int hour;

double temperature;

// read structured in

while (ist >> hour >> temperature) {

if (hour < 0 || 23 <hour) throw range_error("hour out of range");

// fill vector

temps.push_back(Inputdata{hour,temperature});

}

strucktruriert ausgeben

// set brackets for clearer structure

for (int i=0; i<input.size(); ++i)

ost << '(' << input[i].hour << ','

<< input[i].temperature << ")\n";

…

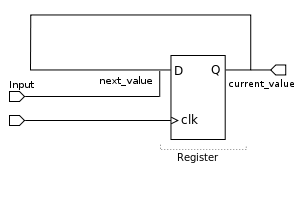

Inputdaten müssen teilweise abgelegt werden. Wie wird dies in VHDL umgesetzt?

-- input signal s_next_value: std_logic_vector(7 downto 0); -- gespeichert signal s_current_value: std_logic_vector(7downto0);

-- input in ff-signal ablegen s_next_value <= input; -- input speichern input_register: process (all) begin . if (reset = '1') then . s_current_value <= (others => '0'); . elsif (clk'event) and (clk = '1') then . -- ausgang ff erhält eingang ff . s_current_value <= s_next_value; . end if; end process;

Normalerweise wird das Inputsignal nicht asynchron an den Eingang des Flip-Flops gelegt. Oft entscheidet ein enable_signal, wann die Daten vor den Eingang gelegt werden sollen. (Dies geschieht mit einem Multiplexer.)

-- input speichern

input_register: process (all)

begin

. if (reset = '1') then

. s_current_value <= (others => '0');

. elsif (clk'event) and (clk = '1') then

. -- ausgang ff erhält eingang ff

. s_current_value <= s_next_value;

. if (s_enable = '1') then

s_next_value <= input;

else

s_nex_value <= s_current_value;

end if;

. end if;

end process;

GPU ist ein Grafikprozessor. Also ein Prozessor, mit spezifischem Profil. Hersteller sind Intel, AMD und Nvidia.

CPU <-> GPU

Wird von einem Host gesprochen, meint man damit die CPU (inkl. Memory). Ein C-Programm läuft auf dem Host.

Cuda <-> Metal

Cuda ist das Framework und die Sprache von Nvidio. Will man eine GPU für ein iOS konfigurieren, so braucht man metal als Framework und swift als Sprache.

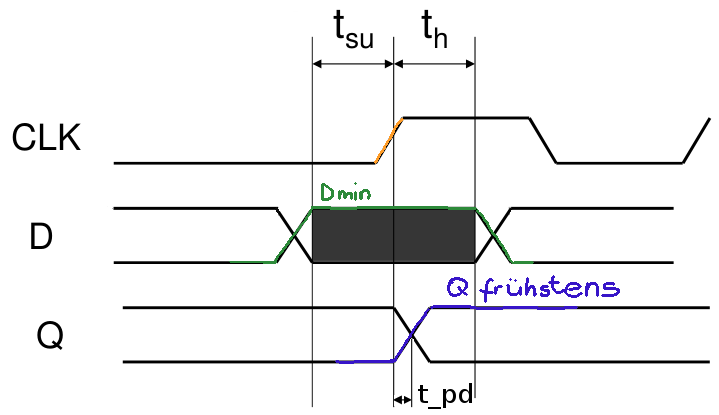

Wechselt das Inputsignal eines Flip-Flops zur falschen Zeit, ist das Ausgangssignal unsicher. Im besten Fall nimmt der Ausgang dann einen selbst gewählten Wert an (Q ode Q), im schlechten Fall „hängt“ sich das Flip-Flop „auf“ und toggelt permanent zwischen Q und Q.

Kritische Zeit beim Eingang

t_setup: so lange müssen Daten vor dem Clock da sein

. (3 bis 12 ns. Cyclone IV: 8 – 10 ns)

t_hold: so lange müssen Daten nach dem Clock anliegen (0 bis 1 ns)

. Diese Zeit muss grösser sein, als die Durchlaufverzögerung des FF.

t_pd: Durchlaufverzögerung: Zeit der Daten, bis sie am Ausgang anliegen.

Treffen neue Daten vor der minimalen Haltezeit ein, so ist unklar, was am Ausgang anliegt.

Ursache für das Nichteinhalten der t_su

Die Clk-Frequenz hängt vom längsten Verzögerungspfad ab. Ist der eingestellte CLK schneller, so kommt bei mindestens einem FF die Daten zu spät an. Die t_su kann dort nicht eingehalten werden.

Warum ist (nur ein) FF bereits ein Problem?

Weil das FF im schlimmsten Fall zu Toggeln beginnt. Dadurch erhalten alle nachfolgenden FF toggelnde Signale und die ganze Linie ist unbrauchbar.

Ein metastabiles FF zieht die anderen FF mit sich.

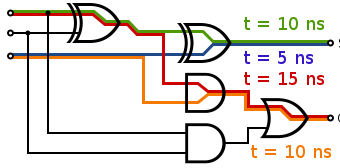

Durchlaufverzögerung (propagation delay)

Ein Signal am Eingang erscheint (theortisch) direkt Ausgang. Real jedoch hat jedes Signal eine Gatter- oder Flip-Flop-Verzögerung.

Verzögerung bei Logik

Jedes Gatter braucht eine kurze Zeit, um die Logik auszugeben. Diese nennt man Gatter-Verzögerung bzw. auf englisch progagation delay.

Nimmt man pro Gatter eine Verzögerung von 5 ns, so hat man nach 3 Gattern einen Pfad von 15 ns.

Verzögerung bei Flip-Flop

Auch jedes Flip-Flop hat nach dem Clk noch eine Verzögerung. Das Signal liegt nicht unmittelbar nach dem Clk am Ausgang an.

Die Verzögerung (t_pd) darf nicht zu lange sein, weil sonst das Signal nicht mehr anliegt. Die Regel ist, dass die Verzögerung küzer sein muss, als die minimale Haltezeit des Signal (t_hold). Bei den Flip-Flops muss zusätzlich noch die Zeit vor dem Clock berücksichtig werden (t_setup). Mehr dazu unter Metastabilität.

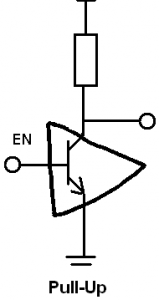

Tristate ist die Zustandsbezeichnung von digitalen IOs. Diese können den Zustand ‚0‘, ‚1‘ oder (je nach Verdrahtung) ‚Z‘ oder ‚Z‚ sein. Der Grund dafür ist, dass Ausgänge getrieben werden müssen, was Transistoren bedingt. Diese können in der Luft hängen und dadurch den dritten Zustand erzeugen.

Pull up (‚Z‘)

Im Ruhezustand fehlt die Verbindung zu GND, aber die Verbindung zu VCC ist über den Widerstand gegeben.

Im Ruhezustand erhält der Ausgang aufgrund der Verbindung mit VCC einen definierten Zustand: logisch HIGH.

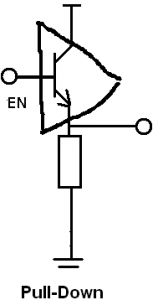

Pull down (‚Z‚)

Im Ruhezustand erhält die Leitung durch die Verbindung zu GND einen klaren Zustand: Logisch LOW.

Transistoren vor IO

In der Digitaltechnik müssen IOs getrieben werden. Das heisst, dass der Input nicht „von selbst“ an den Ausgang übertragen wird, sondern nur, verstärkt den Zustand übergeben kann. Dazu dienen Transistoren.

IO-Logik hat deshalb nicht nur zwei, sondern drei Leitungen zu verwalten (In, Out und enable).

Zustand des Ausgangs

Durch das Transistoren-Bild sieht man, dass der Output, beim Nichtleiten, vom Rest abgehängt ist. Aus diesem Grund gibt es in der Digitaltechnik für die IOs den dritten Zustand ‚Z‚, was so viel wie in der Luft hängen bez. hochomig bedeutet.

Diese gute Visualisierung habe ich von folgender Website.

Putty

Ist eine freie Software zum Zugreifen auf Rechner via SSH (secure Shell), Telnet, Remote login oder über eine serielle Schnittstelle.

Kopieren von Daten

pscp <user>@<ip>:<pfad>/<datei> C:\\home\<user>\<pfad>\<datei>

Daten werden vom anderen Rechner (user, ip) auf den Windows-Rechner verschoben.