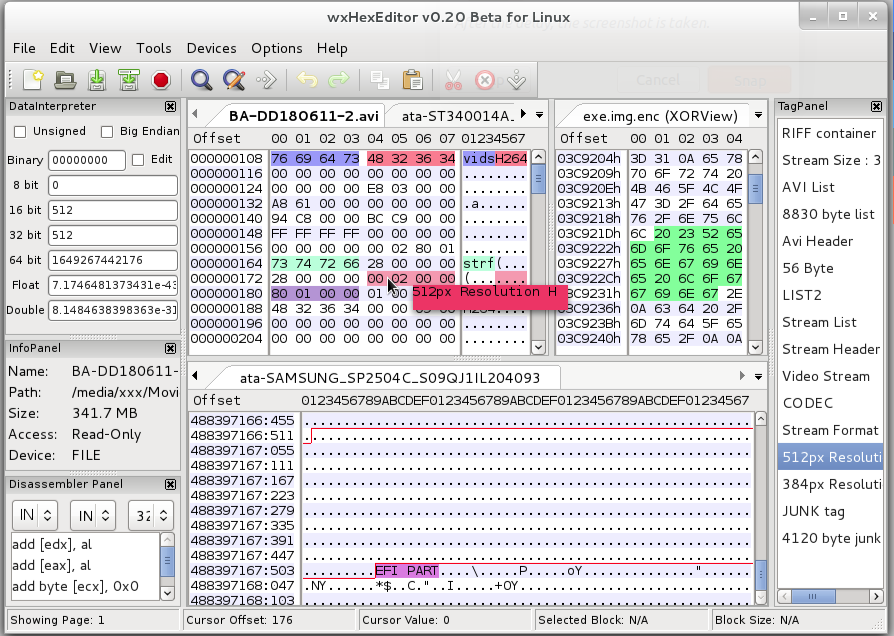

Dieser Hex-Editor zeichnet sich über mächtige Speicheroptionen aus:

- Die Hexwerte können mit Speicheroffset gespeichert werden

- Hexwerte können mit ASCII-Interpretation gespeichert werden

- Hexwerte können als C-Array mit einer wählbaren Datengrösse (int8_t, int16_t, int32_t, ..) gespeichert werden

Dies erleichtert die Weiterverarbeitung der eingelesenen Daten.

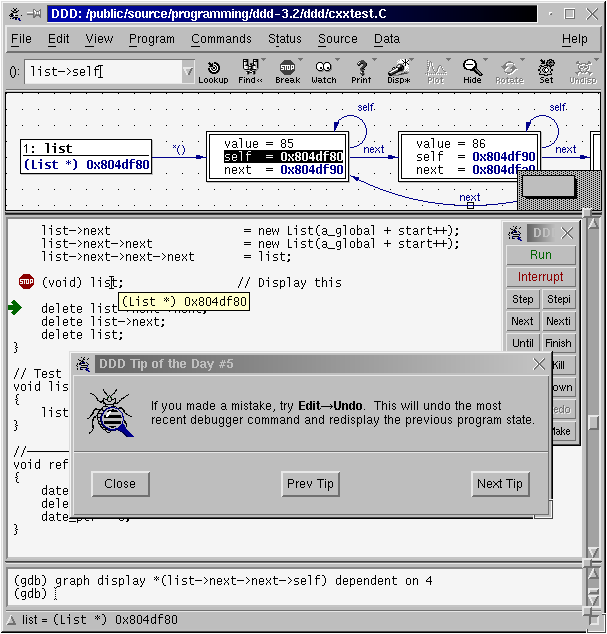

Debuggen von Speicher

Der Inhalt des Speichers (z.B.) eines Arrays muss in ein File kopiert werden. Das File wird eingelesen.

Im Menu können unter VIEW unterschiedliche Fenster (Pannel genannt) aktiviert werden.

Linke Fenster

Zeigt die selektierten Daten in unterschiedlichen Formaten an (Pannel Dateninterpreter) und in der Mitte das Infopannel.

Hauptfenster oben

Mehrere Files können parallel angezeigt werden.

Hauptfenster unten

Ist die Ascii Interpretation des Inhalts. Das Pannel wird TextControl genannt.