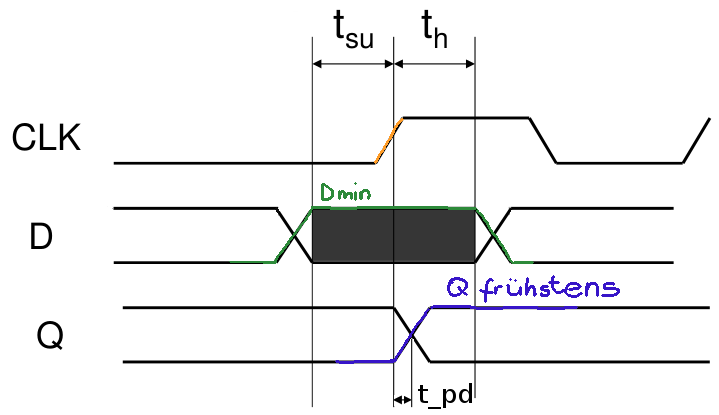

Wechselt das Inputsignal eines Flip-Flops zur falschen Zeit, ist das Ausgangssignal unsicher. Im besten Fall nimmt der Ausgang dann einen selbst gewählten Wert an (Q ode Q), im schlechten Fall „hängt“ sich das Flip-Flop „auf“ und toggelt permanent zwischen Q und Q.

Kritische Zeit beim Eingang

t_setup: so lange müssen Daten vor dem Clock da sein

. (3 bis 12 ns. Cyclone IV: 8 – 10 ns)

t_hold: so lange müssen Daten nach dem Clock anliegen (0 bis 1 ns)

. Diese Zeit muss grösser sein, als die Durchlaufverzögerung des FF.

t_pd: Durchlaufverzögerung: Zeit der Daten, bis sie am Ausgang anliegen.

Treffen neue Daten vor der minimalen Haltezeit ein, so ist unklar, was am Ausgang anliegt.

Ursache für das Nichteinhalten der t_su

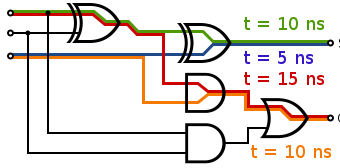

Die Clk-Frequenz hängt vom längsten Verzögerungspfad ab. Ist der eingestellte CLK schneller, so kommt bei mindestens einem FF die Daten zu spät an. Die t_su kann dort nicht eingehalten werden.

Warum ist (nur ein) FF bereits ein Problem?

Weil das FF im schlimmsten Fall zu Toggeln beginnt. Dadurch erhalten alle nachfolgenden FF toggelnde Signale und die ganze Linie ist unbrauchbar.

Ein metastabiles FF zieht die anderen FF mit sich.