signal s_midi_out: std_logic_vector(7 downto 0);

s_midi_out <= "1 0 0 1 1 0 1 0";

7,6,5,4,3,2,1,0

s_midi_out(7) enthält den Wert ‚1‘

s_midi_out(0) enthält den Wert ‚0‘

s_midi_out(5 downto 3) enthält die Werte „011“

signal s_midi_out: std_logic_vector(7 downto 0);

s_midi_out <= "1 0 0 1 1 0 1 0";

7,6,5,4,3,2,1,0

s_midi_out(7) enthält den Wert ‚1‘

s_midi_out(0) enthält den Wert ‚0‘

s_midi_out(5 downto 3) enthält die Werte „011“

Operiert man mit Indexes, Adressen, etc. so ist dies am einfachsten mit dez. Zahlen:12 + 100 = 112;

Das selbe gilt auch für die Zähler.

VHDL hat dafür 3 Types: integer, unsigned, natural .

signal addr: integer range 0 to 15; addr <= to_integer(value_a);

Adresse kann Werte von 0, 1, 2, … 15 annehmen.

cnt: integer range 0 to 3;

Der Zähler zählt 0, 1, 2, 3 und beginnt wieder bei 0.

.

2. Unsigned

-- 5 Werte signal count: unsigned(4 downto 0); signal value_a: unsigned(15 downto 0); signal value_b: unsigned(15 downto 0);

Der Zähler kann die Werte 4, 3, 2, 1, und 0 annahmen. Er besitzt 5 Zustände.

value_b <= to_unsigned(max_value, 4); ????? not shure

.

3. Natural

CONSTANT max_value: natural := 200; signal s_reg_index: natural; signal s_next_reg_indes: natural;

s_next_reg_index := s_reg_index + 1;

Zuweisung braucht ein : vor dem = line_cnt := line_cnt + 1; reset := 1;

…

Was ist der Unterschied dieser Zeichen?

&: vektor zusammensetzen

s_midi <= s_tone_on & s_note_value & s_velocity;

– geht nur für std_logic;

.

AND: logisch zusammenzählen

Das AND folgt der Logik des Gatters AND:

Nur zwei ‚1‘ geben eine ‚1‘, alles andere gibt eine ‚0‘;

s_result = s_enable and s_bit_input;

– geht nur für std_logic;

– ist üblich für Signal-Logik und Takt-Logik

if (strobe_i = '1' and clk_intern = '0') then . // do

.

+: normal zählen

– geht nur für unsigned, integer, natural

signal index: integer range 0 to 15 := 0; signal offset: integer range 0 to 255 := 100; index <= to_integer(s_midi(7 downto 4)); new_index = index + 4; addr <= index + offset;

– ist bei Zählern üblich

next_cnt <= cnt + 1;

..

In VHDL ist es üblich, vor dem Senden von Daten mehrere Informationen (Signale) in einen grossen Vektor zusammenzubauen.

Beim Empfangen wird dann der grosse Vektor wieder in seine Einzelteile zerlegt.

1. Einzelne Signalgrössen

signal s_tone_on: std_logic; signal s_note_value: std_logic_vector(7 downto 0); signal s_velocity: std_logic_vector(7 downto 0); signal s_midi: std_logic_vector(16 dowonto 0);

2. Addition zu Vektor

// Vektor für innerhalb Entity bilden

s_midi <= s_tone_on & s_note_value & s_velocity;

// oder direkt beim Port

GPIO_0 <= s_tone_on & s_note_value & s_velocity;

Man kann auch nur Teile des Vektors addieren.

Oft ist ein Vektor aus mehreren Informationen zusammengesetzt (vgl midi_in).

entity a is

port( midi_in: in std_logic_vector(16 downto 0);

data: out std_logic_vector(7 downto 0)

);

Braucht man nun nur einen Bit-Abschnitt so geschieht dies so:

1. Signal von der gewünschten Bit-Breite definieren

signal s_tone_on: std_logic; signal s_note_value: std_logic_vector(7 downto 0); signal s_velocity: std_logic_vector(7 downto 0);

2. Vektor bitweise zuweisten

s_tone_on <= midi_in(16); s_note_value <= midi_in(15 downto 8); s_velocity <= midi_in(7 downto 0);

….

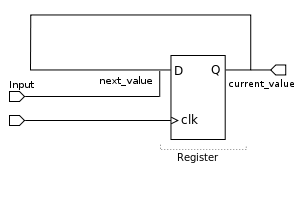

Inputdaten müssen teilweise abgelegt werden. Wie wird dies in VHDL umgesetzt?

-- input signal s_next_value: std_logic_vector(7 downto 0); -- gespeichert signal s_current_value: std_logic_vector(7downto0);

-- input in ff-signal ablegen s_next_value <= input; -- input speichern input_register: process (all) begin . if (reset = '1') then . s_current_value <= (others => '0'); . elsif (clk'event) and (clk = '1') then . -- ausgang ff erhält eingang ff . s_current_value <= s_next_value; . end if; end process;

Normalerweise wird das Inputsignal nicht asynchron an den Eingang des Flip-Flops gelegt. Oft entscheidet ein enable_signal, wann die Daten vor den Eingang gelegt werden sollen. (Dies geschieht mit einem Multiplexer.)

-- input speichern

input_register: process (all)

begin

. if (reset = '1') then

. s_current_value <= (others => '0');

. elsif (clk'event) and (clk = '1') then

. -- ausgang ff erhält eingang ff

. s_current_value <= s_next_value;

. if (s_enable = '1') then

s_next_value <= input;

else

s_nex_value <= s_current_value;

end if;

. end if;

end process;

Ein alter commit wurde heruntergeladen. Nun ist der Head losgelöst.

temporären Branch erstellen

git checkout -b develop2

Dadurch wird der losgelöste HEAD an den neuen Branch gebunden!

Als Überblick ev. git diff master develop2 .

Branch Master zufügen

Danach normal weitergehen (mit diesem Branch),

oder den Branch zum Mater oder anderen Branch einbinden.

git branch -f master develop2 git checkout master git branch -d develop2

…

struct ImageInt16 {

. short data[100]

};

Objekt bilden

2 Bilder werden abgelegt. Inhaltstruktur ist identisch. Der Typ der Speichervariable nicht.

ImageInt16 bild_1; // enthält Wert ImageInt16* bild_2; // enthält Speicherort, an dem Wert liegt

Variable auslesen

int result_1, result_2; result_1 = bild_1.data[0]; result_2 = bild_2->data[1]; // Objektreferenz //oder result_2 = (*bild_2).data[1]; // Dereferenziert . // Wert des Objekts

Der ersten zwei Wert aus dem Array wurden übergeben.

..

Arithmetic if

Mit weniger schreiben, dasselbe erhalten

temp = 32 ? summer : winter;

Zuerst folgt ein Vergleich (vor dem?) .

Ist der Vergleich wahr, so folgt die Anweisung nach dem ?

Ist der Vergleich falsch, dann folgt die zweite Anweisung.

<compare> ? < ja > : <nein>;

..

In C++ gehören die „enums“ zu den Klassen. Sie sind ein Sonderfall einer Klasse, da sie keine Funktionen, sondern nur Konstanten haben.

– enums beginnen bei 0, ausser:

– wird der ersten Konstante einen Wert zugewiesen, beginnt der

. enum bei dieser Zahl und zählt immer +1.

enum class Month{

. jan

. feb,

. ...

. dez

};

enum class gruppe_1{

. urs,

. noe,

. ...

. eva

};

Zuweisungen

gruppe_1 karl = 5; // neuer Wert dazu gruppe_1 nils = gruppe_1.eva // nils an Stelle von eva

Operationen mit Enumerates

Month new_month = sept; ++new_month; //new_month is now okt ++new_month; //new_month is now nov

Bjarne 9.6

…