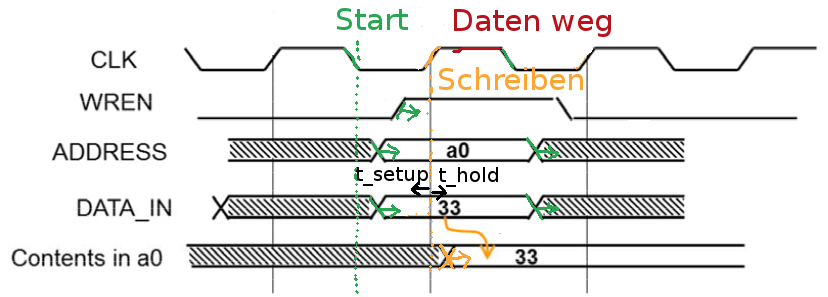

Das Timing (einhalten der Setup- und Hold-Zeit) ist eine Fehlerquelle für ungültige Daten.

Bsp. eines Schreibe-Zyklus

– Ein neuer Zylkus beginnt bei der fallenden Flanke

Da Daten leicht verzögert ankommen, beginnt der neue Zyklus

nach der fallenden Flanke. Die Verzögerung darf nicht so gross sein,

dass die setup Zeit verletzt wird.

(t_setup = Zeit, in der Daten vor CLK anliegen müssen)

– Ausführen des Befehls bei steigender Flanke

Hier ist es ein Schreibbefehl. Auch der Lesebefehl wird bei steigender Flanke

ausgeführt.

Der Befehl wird leicht verzögert ausgeführt.

Um den Befehl recht auszuführen, darf die Hold Zeit nicht verletzt werden.

(t_hold = Zeit, in der die Daten nach dem CLK noch anliegen müssen)

Bereits kurz nach der ausführenden Flanke sind die Daten wieder Weg und der neue Zyklus beginnt.

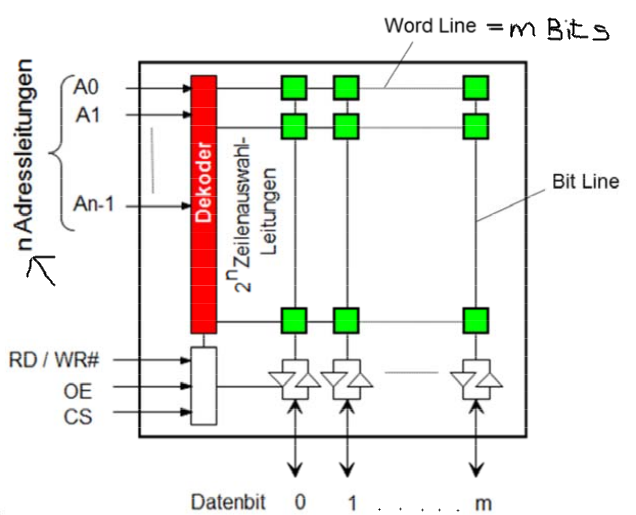

FPGA

Speicher haben intern einen Takt. Dadurch entfällt das Timingproblem.