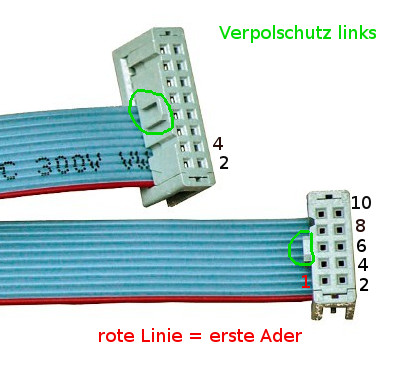

- Die markierte Linie ist die erste Ader

- Der Verpolschutz sagt, wo die 1 ist.

- Die Nr. 2 ist auf der anderen Seite, als der Verpolschutz

TI stellte ein Board mit 10 Sensoren und App zur Verfügung, das CC26050STK Starter Kit.

Sensoren

Umgebungs- und Objekttemperatur, Feuchtigkeit, Druck, Höhe, Bewegung (neun Achsen), Geschwindigkeit, Drehzahl, Magnet und Licht.

Sensordaten auf Cloud

Mit der App können die Daten über die Cloud ausgelesen und weitergeleitet werden.

Entwickler Erweiterung

Zum Sensor Board gibt es eine Erweiterung für Entwickller: das SimpleLink SensorTag DevPack. Die Erweiterung beinhaltet ein JTAG Schnittstelle und eine IDE zum Debuggen und Programmieren.

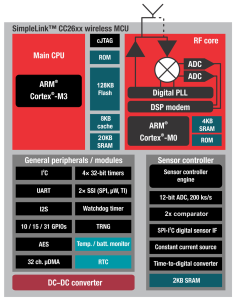

Komponenten des Sensor Board

– zwei Prozessoren:

– zwei Prozessoren:

M3 als CPU und

M0 für RF (BLE )

– JTAG zum Programmieren/Debuggen

– Schnittstellen UART, I2S, SPI

– Sensor Controller

Datenblatt und Beschreibung

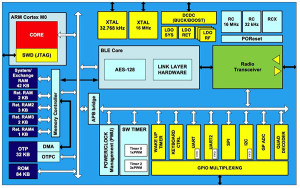

Der RF Chip DA14580

– Braucht zum Senden 4.9 mA.

– Braucht zum Senden 4.9 mA.

– Braucht im Sleep Mode nur 600nA.

– Betriebsspannung von 0.9 V.

– Hat JTAG Schnittstelle (SWD)

– Hat einen BLE Core mit AES-128

für Single Mode

Je nach dem, welches Protokoll man benutzen will, wird ein anderer protocol stack heruntergeladen.

Ist eine Erweiterung zum SimpleLink Wireless Board von TI für niedere Datenraten mit dem Prozessor CC2650.

Bei der Konfiguration des Peripherie-Gerätes zeigen sich die Spezialfunktionen des BLE-Standards.

Die Funktionalität wird um die Batterie-Versorgung herum aufgebaut. Es gibt drei Arten, mit dem zentralen Gerät zu Kommunizieren:

Optimizing for Low Power (14.8)

– Beste Advertizing Channel Intervall definieren

– Beste Verbindungszeit definieren

– Schnellste Attribut (=Daten)-Aufnahme einrichten

Zur Analyse der Übergänge kann ein State Diagramm genommen werden. Gestartet wird im ausgeschaltenen Modus. (In diesem Zustand sollte sehr wenig Leistung verbraucht werden.)

Wird das Peripherie-Geräte für BLE angestellt, geht es in den discoverable (14.3)-Zustand über. Das zentrale Gerät verbindet sich.

Wie baut der RF Chip 18xx eine Verbindung zu einem BLE-Gerät auf ?

Informationen aus der iOS Developper Library

Glossar

– Der RF Chip (angebunden an einen Processor und an einen Sensor) gilt als Peripheral Device. Die Daten werden von hier gesendet. Das Peripheral Device hat Serverfunktion.

– Das Tablet, das die Daten empfängt wird Central Device genannt. Es befindet sich im Client Modus.

Kommunikation Peripheral Device (CH 14)

Hat das Periphier-Gerät Daten, sendet es broadcast advertizing packets. Meldet, dass es Daten gibt. Diese Kommunikation geschieht auf den 3 advertizing channels.

![]()

Kommunikation des Central Device (Ch 13)

Das Tablet scanned auf allen advertizing channels und schaut, ob irgendwo interessante Daten liegen. Wenn ja, wird eine Verbindung aufgebaut. Es gibt 2 Scan-Zustände: passives oder aktives Scannen. Im passiven hört das zentrale Gerät, ob irgend ein Peripherie-Gerät Daten zur Verfügung stellt. Im aktiven Modus ist das zentrale Gerät, nachdem es ein Gerät detektiert hat. Im aktiven Modus werden mehr Informationen angefordert.

Das periphere Gerät teilt der Zentrale den Namen des Geräts und eine Geräte-ID mit.

Datenstruktur Peripheral

Ein Peripheriegerät stellt eine Anzahl an Services zur Verfügung. Sobald eine Verbindung zum zentralen Gerät besteht, können Daten aus diesen Services übernommen werden.

Service: Daten (inkl. Verhaltensinformationen) zum Ausführen eines Befehls, eines Dienstes. Ein Service beinhaltet mehrere Characteristics (und teilweise auch andere Services).

Characteristics: Detailangaben vom Peripheriegerät.

Zentrales Gerät erhält Daten

Besteht eine Verbindung, kann das zentrale Gerät sowohl Daten lesen wie auch selbst Werte schreiben. Die Daten (Services) werden im Core Blootooth framework abgelegt und verarbeitet. Fast alle BLE Aktionen geschiehen in diesem Gerät.

..

Funktionsweise

Jedes Bit wird in eine Speicherzelle (FET) gespeichert. Im Gegensatz zum FPGA ist diese Speicherzelle nicht flüchtig.

Ansteuerung

Wie bei RAMs: über eine Matrixordnung. Es wird Zeilenweise oder in ganzen Sektoren gespeichert. Jede Zeile entspricht einem Word einer bestimmten Bit-Länge.

Man spricht FLASH Speicher selten direkt an, sondern nutzt Schnittstellen.

Im Embedded Bereich

Brauchen einen externen Speicherplatz zum Speichern von Daten oder zum Booten des Betriebssystems und der Applikationen. Flash-Speicher werden ROMs vorgezogen, da man diese auswechseln kann. Dadurch ist ein Update der Firmware möglich, was beim ROM nicht der Fall ist. Eine SD-Karte (ebd. ein Flash Speicher) ist eine Alternative zu Flash-ICs.

Spezialitäten

– sind langsam

– können auch als HD-Ersatz genommen werde

– EEPROMs sind die bekanntesten Flash Speicher

– Jeder USB-Stick hat einen Flash-Speicher und einen Microkontroller

Überblick der Funkionen

Der Audio Codec gibt die Audiodaten aus. Zudem verwaltet er alle Audio-Pfäde auf dem Board. Er definiert, ob der Analoge Input aktiv oder der Digitale Input übergangen wird. Alle Einstellungen stehen in seinen Registern.

Bidirektionale Konfiguration des Audio Codec IO-Bauteilen

Die Einstellungen des Audio Codecs erfolgen über Register. Damit die Register gesetzt werden können, wird mit I2C auf die Codecregister zugegriffen.Insgesamt bestehen 11 Register mit je 16 Bits.

Einerseits werden über den Codec Kontroller die Konfigurationen gesetzt, anderseits setzt der Audio Codec die Pfade aktiv oder nicht. Die Kommunikation ist bidirektional: in beide Richtungen.

Audio Codec mit Audio-Daten speisen

Die konkrete Musikdatei wird über I2S dem Codec übermittelt und dann an den entsprechenden Ausgang geleitet.

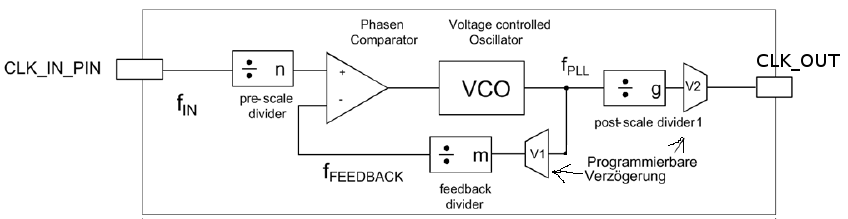

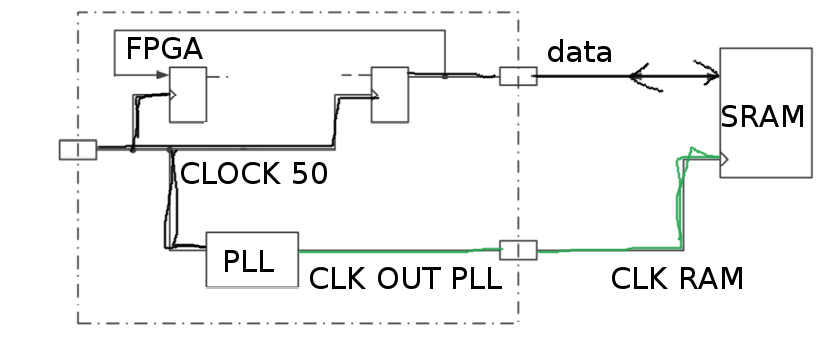

In den FPGAs sind PLLS ein Standard für zwei Gründe:

– Um Pfadverzögerungen zu Kompensieren (Bsp. 2)

– Um andere Taktfrequenzen zu erhalten (Bsp. 1)

Neuer Takt

Viele Protokole besitzen ihre eigene Takt-Frequenz. Daher braucht es einige Takte innerhalb eines FPGAs

f_out = (f_in * m) / n // m wird multipliziert, n und g dividiert

Kompensation Verzögerung

Werte im Feedback Pfad v1= 3 ns schieben CLK_IN nach vorne,

Werte beim Ausgang v2 = 8 ns verzögern CLK_IN.

Bsp Kompensation

Ausgangslage: Durch Flip-Flop-Verzögerung oder Pfadverzögerung und IO-Verzögerung kommt data 5ns später als CLK_50 beim SRAM an.

1.) Entweder führt man ein PLL in den data-Pfad ein,

dann muss der PLL den CLK_50 vorverlegen v1 = 5 ns

um die Verspätung zu kompensieren,

oder (siehe Bild)

2.) man verzögert den CLK_50 zum SRAM mit genau der Verzögerung,

die der data-Pfad hat v2 = 5 ns . Dann kommt CLK RAM „gleich verzögert “

wie data beim SRAM an.

PLL Rechenbeispiel mit Takterzeugung und Verzögerung

..

Grundstruktur Datenablage

Ein ausführbares Programm (*.exe) teilt seine Daten in vier Segmente ein: *.code, *.data, *, heap und Stack.

Codesegment

Liegt bei der tiefsten Adresse. Hier liegt der Maschinencode. Häufig liegen hier auch die Konstanten. Das Codesegment kann mit einem Schreibschutz versehen werden, also nur gelesen werden.

Datensegment

Hier liegen die initialisierten globalen Variablen sowie wenn eine lokale Variable als static definiert wurde. Sind Variablen nicht initialisiert, so liegen sie im BSS Segment.

Heap

Enthält nur dynamische Variablen, die mit malloc() zur Laufzeit generiert und wieder gelöscht werden.

Stack

Legt alle sich ändernden Daten zur Laufzeit ab und holt sie permanent wieder. Ständiges Wechseln der Daten. Deshalb braucht es einen Stack Pointer, der jeweils die aktuelle Speicherstelle weiss.

Der Stack liegt an der höchsten Adresse.

Im Stack liegen alle lokalen Variablen.