RN 42 Microchip

Funktionsweise

Jedes Bit wird in eine Speicherzelle (FET) gespeichert. Im Gegensatz zum FPGA ist diese Speicherzelle nicht flüchtig.

Ansteuerung

Wie bei RAMs: über eine Matrixordnung. Es wird Zeilenweise oder in ganzen Sektoren gespeichert. Jede Zeile entspricht einem Word einer bestimmten Bit-Länge.

Man spricht FLASH Speicher selten direkt an, sondern nutzt Schnittstellen.

Im Embedded Bereich

Brauchen einen externen Speicherplatz zum Speichern von Daten oder zum Booten des Betriebssystems und der Applikationen. Flash-Speicher werden ROMs vorgezogen, da man diese auswechseln kann. Dadurch ist ein Update der Firmware möglich, was beim ROM nicht der Fall ist. Eine SD-Karte (ebd. ein Flash Speicher) ist eine Alternative zu Flash-ICs.

Spezialitäten

– sind langsam

– können auch als HD-Ersatz genommen werde

– EEPROMs sind die bekanntesten Flash Speicher

– Jeder USB-Stick hat einen Flash-Speicher und einen Microkontroller

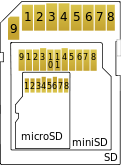

Als externer Speicherplatz kann eine SD (Secure Digital Memory) Karte genommen werden. Es gibt die Mini- und Micro-Ausführung.

Spezialitäten

– Ihr Speicherprinzip ist die Flash-Speicherung.

– Speicherbereich kann partitioniert werden:

In einem Teil liegt ein System-Image, im anderen Teil das File Sytem

– besitzt einen internen Controller

– 9 Kommunikationspins

– SD-Karten mit integriertem WLAN oder GPS

– SD-Karte mit USB-Stecker Typ A (normaler Stecker) zum Anschliessen

In Enbedded Systemen

Das Betriebssystem und die Applikatins Software wird meist in Flash Speichern abgelegt und von dort gebootet. Man kann aber auch eine genug grosse SD-Karte zum Booten des Systems nehmen.

Kommunikation

Die Kommunikation basiert auf dem SPI-Prinzip.

– Initialisierungssequenz:

– Initialisierungssequenz:

Schützt vor unberechtigtem Zugriff auf die Daten

– Pin 1: Kartenerkennung (Dateinleitung 3)

– Pin 2: Kommandos (Befehl/Antwort)

– Pin 3/6: GND

– Pin 4: VCC

– Pin 5: CLK

– Pin 7/8/9: Data (Datenleitung 0, 1, 2)

Singalport

Traditionall wird auf einem Speicher entweder geschrieben oder gelesen werden. Dies geschieht nicht gleichzeitig.Es handelt sich um einen Singel Port Speicher.

Dualport (z.B. in FPGAs)

Auf denselben Speicher wird über zwei Schnittstellen zugegriffen. Dadurch kann zeitgleich auf denselben Speicher gelesen wie geschrieben werden.

Bei der Dualport-Konfiguration sagt man, welche Aktion Priorität hat, falls lesen und schreiben auf die selbe Adresse getätigt werden soll.

Vorteile des Dualport

– lesen und schreiben können einen anderen Takt haben

– lesen und schreiben können andere Datenbreiten haben

Implementation

Dualport ist nur durch 2 unabhängige Bussysteme möglich. Beide Ports werden an einen Bus manuell angebunden. Ebenso wird beim FPGA in der Konfiguration der Ports in den IP-Einstellungen minutiös eingestellt.

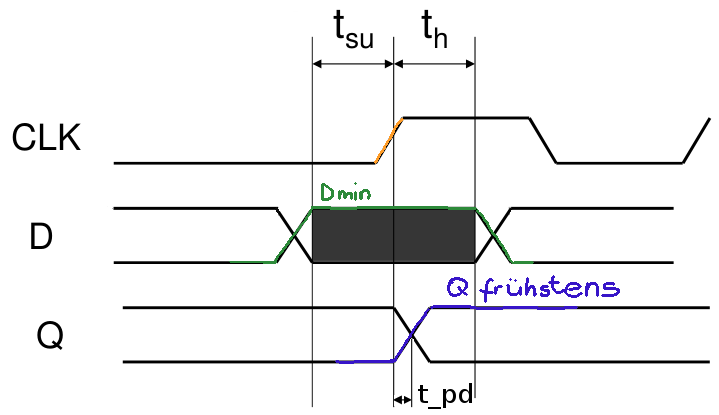

Wechselt das Inputsignal eines Flip-Flops zur falschen Zeit, ist das Ausgangssignal unsicher. Im besten Fall nimmt der Ausgang dann einen selbst gewählten Wert an (Q ode Q), im schlechten Fall „hängt“ sich das Flip-Flop „auf“ und toggelt permanent zwischen Q und Q.

Kritische Zeit beim Eingang

t_setup: so lange müssen Daten vor dem Clock da sein

. (3 bis 12 ns. Cyclone IV: 8 – 10 ns)

t_hold: so lange müssen Daten nach dem Clock anliegen (0 bis 1 ns)

. Diese Zeit muss grösser sein, als die Durchlaufverzögerung des FF.

t_pd: Durchlaufverzögerung: Zeit der Daten, bis sie am Ausgang anliegen.

Treffen neue Daten vor der minimalen Haltezeit ein, so ist unklar, was am Ausgang anliegt.

Ursache für das Nichteinhalten der t_su

Die Clk-Frequenz hängt vom längsten Verzögerungspfad ab. Ist der eingestellte CLK schneller, so kommt bei mindestens einem FF die Daten zu spät an. Die t_su kann dort nicht eingehalten werden.

Warum ist (nur ein) FF bereits ein Problem?

Weil das FF im schlimmsten Fall zu Toggeln beginnt. Dadurch erhalten alle nachfolgenden FF toggelnde Signale und die ganze Linie ist unbrauchbar.

Ein metastabiles FF zieht die anderen FF mit sich.

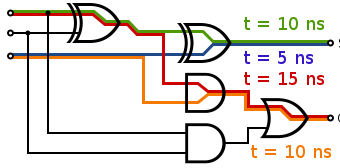

Durchlaufverzögerung (propagation delay)

Ein Signal am Eingang erscheint (theortisch) direkt Ausgang. Real jedoch hat jedes Signal eine Gatter- oder Flip-Flop-Verzögerung.

Verzögerung bei Logik

Jedes Gatter braucht eine kurze Zeit, um die Logik auszugeben. Diese nennt man Gatter-Verzögerung bzw. auf englisch progagation delay.

Nimmt man pro Gatter eine Verzögerung von 5 ns, so hat man nach 3 Gattern einen Pfad von 15 ns.

Verzögerung bei Flip-Flop

Auch jedes Flip-Flop hat nach dem Clk noch eine Verzögerung. Das Signal liegt nicht unmittelbar nach dem Clk am Ausgang an.

Die Verzögerung (t_pd) darf nicht zu lange sein, weil sonst das Signal nicht mehr anliegt. Die Regel ist, dass die Verzögerung küzer sein muss, als die minimale Haltezeit des Signal (t_hold). Bei den Flip-Flops muss zusätzlich noch die Zeit vor dem Clock berücksichtig werden (t_setup). Mehr dazu unter Metastabilität.

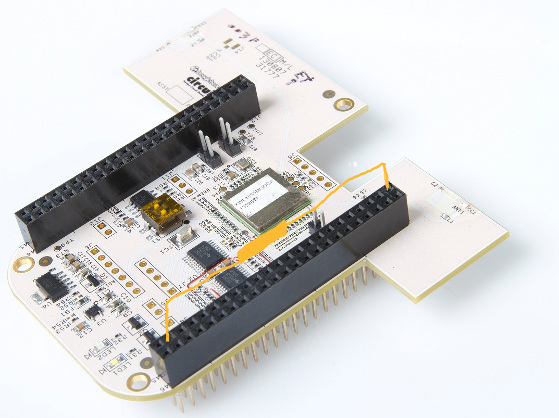

Beagle Bones sind von Texas Instruments. Sie sind die professionellere Variante der Arduinos und eine Alternative zu den Raspberry Pi.

Implementation des WLAN-Chips WL183x

Zum Testen dieses Chips, ist das Beagle Bone eine gute Idee.

Die Prozessoren sind von ARM, dieses Modell hat HDMI ist ist bezüglich Kommunikation sehr vielseitig. Gleichzeitg ist das Board energiesparend konzipiert.

Das WLAN- und Bluetooth-Cap ist für durchsatz-starkes WLAN ( 802.11 n) gedacht und hat leistungsstarke Komponenten. Das Cap hat 2 Antennen (MIMO) und kann 40 MHz-Bandbreiten (802.11n) verarbeiten.

Bei Bluetooth ist BLE implementiert und die Coexistenz von BLE und WLAN ist möglich. Ein eigener, freier Datenstack ist vorhanden

Das Timing (einhalten der Setup- und Hold-Zeit) ist eine Fehlerquelle für ungültige Daten.

Bsp. eines Schreibe-Zyklus

– Ein neuer Zylkus beginnt bei der fallenden Flanke

Da Daten leicht verzögert ankommen, beginnt der neue Zyklus

nach der fallenden Flanke. Die Verzögerung darf nicht so gross sein,

dass die setup Zeit verletzt wird.

(t_setup = Zeit, in der Daten vor CLK anliegen müssen)

– Ausführen des Befehls bei steigender Flanke

Hier ist es ein Schreibbefehl. Auch der Lesebefehl wird bei steigender Flanke

ausgeführt.

Der Befehl wird leicht verzögert ausgeführt.

Um den Befehl recht auszuführen, darf die Hold Zeit nicht verletzt werden.

(t_hold = Zeit, in der die Daten nach dem CLK noch anliegen müssen)

Bereits kurz nach der ausführenden Flanke sind die Daten wieder Weg und der neue Zyklus beginnt.

FPGA

Speicher haben intern einen Takt. Dadurch entfällt das Timingproblem.

Speicherbreite

Die Speicherbreit ist oft identisch mit der Busbreite.

Ist sie dies nicht, muss mit Byte-enable das Ansprechen geregelt werden.

Word = Breite einer Bit-Zeile (32-Bit, 16-Bit, ..)

= Speicherbreite

. 1 Word hat m Bits.

Bit = Einzelne Speicherzelle.

Speichertiefe

Die Tiefe hängt von der Anzahl Adressleitungen ab.

Führen zum Speicher n Adressleitunge, so ist der Speicher

2^n (Word-)Zeilen tief.

Bsp. 2 Adressleitungen = 4 Speicherzeilen (Words) auslesbar

Speichergrösse

Word-Grösse x Anzahl Zeilen = m x 2^n

Bsp. Word = 32 Bit, 16 Adressleitungen

Speichergrösse: 4 x 2^16 =

4 x 2^3 x 2^3 x 2^10 = 4 x 8 x 8 x 1’000 =

32 x 8’000 = 256 kBytes