Inputdaten müssen teilweise abgelegt werden. Wie wird dies in VHDL umgesetzt?

- man kann per IP RAM anschliessen und dort per Adresse die Daten hineinschreiben.

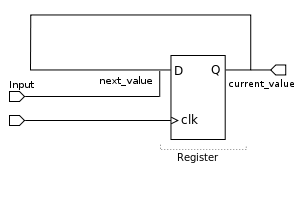

- Das VHDL-eigene Speicherprinzip sind jedoch die Flip- Flops. Alle Daten die gespeichert werden sollen, werden in (Vektoren) von Flip-Flops abgelegt

Signale führen Wert in und aus dem Flip-Flop-- input signal s_next_value: std_logic_vector(7 downto 0); -- gespeichert signal s_current_value: std_logic_vector(7downto0);

-- input in ff-signal ablegen s_next_value <= input; -- input speichern input_register: process (all) begin . if (reset = '1') then . s_current_value <= (others => '0'); . elsif (clk'event) and (clk = '1') then . -- ausgang ff erhält eingang ff . s_current_value <= s_next_value; . end if; end process;

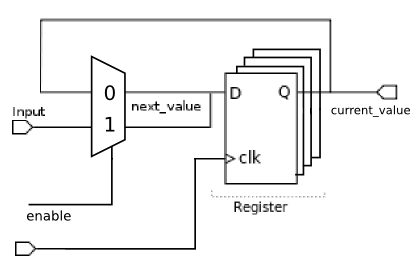

Normalerweise wird das Inputsignal nicht asynchron an den Eingang des Flip-Flops gelegt. Oft entscheidet ein enable_signal, wann die Daten vor den Eingang gelegt werden sollen. (Dies geschieht mit einem Multiplexer.)

-- input speichern

input_register: process (all)

begin

. if (reset = '1') then

. s_current_value <= (others => '0');

. elsif (clk'event) and (clk = '1') then

. -- ausgang ff erhält eingang ff

. s_current_value <= s_next_value;

. if (s_enable = '1') then

s_next_value <= input;

else

s_nex_value <= s_current_value;

end if;

. end if;

end process;