Von der Prüfspitze zu Testpins

Früher wurde ausschliesslich mit der „Nadelmethode“ Testnadeln an ausgewählte Stellen (Knoten) angelötet, um den Signalverlauf zu testen.

Da die Bauteile immer kleiner werden ist dies physisch fast nicht mehr möglich. An den Teststellen (Knoten) werden Leitungen an die Oberfläche fix geführt. Ist dies in einem Chip (Built in) so enstehen Pins am Chip-Ausgang, die Zugang zu den Knoten bieten.

JTAG-Standard

Der IEEE 1149.1 Standard ist von der Gruppe JTAG verfasst und definiert eine Schnittstelle für Boundary Scan Test in Chips. Detailierter Artikel JTAG

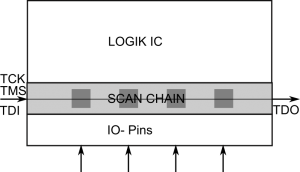

Über die JTAG-Schnittstelle, auch TAP = Test Access Port genannt kann auf die SCAN CHAIN (siehe Boundary Scan) auf die Ein-und Ausgänge des Chips zugegriffen werden.

TAP Schnisstelle

JTAG definiert 4 Signale:

– TCK: Der Clock

– TMS: Der Testmode

– TDI: Die Datenleitung für Input (Simulation)

– TDO: Die Ausgabe des aktuellen Zustands an den Ein-und Ausgängen.

..